Floorplan (microelectronics)

In today's world, Floorplan (microelectronics) is a topic that generates great interest and discussion in different areas. Its relevance transcends borders and its impact is felt in society, the economy and culture. The importance of Floorplan (microelectronics) has led to it being carefully investigated and analyzed in order to better understand its implications and consequences. In this article, we will explore the topic of Floorplan (microelectronics) from different perspectives, with the aim of offering a comprehensive and enriching vision. From its origins to its current state, through its possible future scenarios, Floorplan (microelectronics) is a topic that does not leave anyone indifferent, and that is why it is essential to address it in a deep and thoughtful manner.

In electronic design automation, a floorplan of an integrated circuit consists of a schematic arrangement of its major functional blocks on the chip area and the specification of high-level parameters such as the aspect ratio or core utilization.[1]

The design step in which floorplans are created is called floorplanning, an early stage in the design flow for integrated circuit design.[1]

Various mathematical abstractions of this problem have been studied.[2]

Floorplanning design stage

The floorplanning design stage consists of various steps with the aim of finding floorplans that allow a timing-clean routing and spread power consumption over the whole chip.

- Chip Area Estimation: The dimensions and aspect ratio of the chip area are determined. The estimation considers the space required to place macros, standard cells and I/O ports while also leaving enough space for routing resources to enable a successful place and route design flow. Usually a core utilization of 60%-70% is targeted.[3]

- I/O Pad Positioning: Input/Output Pads usually need to be positioned along the periphery of the chip. Near the I/O Pads space for line drivers needs to be reserved to minimize delay and signal degradation.[4]

- Macro Placement: During macro placement large functional blocks with a fixed size and fixed pins such as memory arrays, clock generators or custom components need to be placed within the floorplan's outline. Effective macro placement minimizes the length of timing critical paths, avoids routing congestion and ensures thermal balance.[4]

- Standard Cell Row Creation: Areas where standard cells should be placed are determined and divided into standard cell rows. During the placement stage standard cells are forced to align with standard cell rows[5] although they might be of multi-row height. The height of the standard cell rows determines the available routing resources per row while also influencing the power.[6]

- Power / Ground Structures: Obtaining a power/ground network is not always included in the floorplanning stage. There are however approaches to cosynthesize floorplans and P/G networks based on the idea that if macros and I/O pads are fixed, a power grid analysis is possible.[7]

Mathematical models

In mathematics floorplanning refers to the problem of packing smaller rectangles with a fixed or unfixed orientation into a larger rectangle.[citation needed] The dimensions of the larger and smaller rectangles might be fixed (hard constraints) or must be optimized (soft constraints). Additionally, a measure modelling the quality of routing that the floorplan allows might be optimized.

Various variants of rectangle packing are NP-hard.[8]

Sliceable floorplans

A sliceable floorplan is a floorplan that may be defined recursively as described below.[9]

- A floorplan that consists of a single rectangular block is sliceable.

- If a block from a sliceable floorplan is cut ("sliced") in two by a vertical or horizontal line, the resulting floorplan is sliceable.

The process is known as guillotine cutting. Sliceable floorplans have been used in a number of early electronic design automation tools[9] for a number of reasons. Sliceable floorplans may be conveniently represented by binary trees (more specifically, k-d trees), which correspond to the order of slicing. More importantly, a number of NP-hard problems with floorplans have polynomial time algorithms when restricted to sliceable floorplans.[10]

-

A sliceable floorplan

-

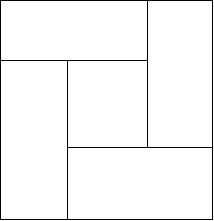

A non-sliceable floorplan

Further reading

- The Chip Planner of the PLAYOUT System

- VLSI Physical Design: From Graph Partitioning to Timing Closure, by Kahng, Lienig, Markov and Hu, doi:10.1007/978-3-030-96415-3ISBN 978-3-030-96414-6, 2022

- Fundamentals of Layout Design for Electronic Circuits, by Lienig, Scheible, Springer, doi:10.1007/978-3-030-39284-0ISBN 978-3-030-39284-0, 2020

References

- ^ a b "Floorplan in VLSI Physical Design". iVLSI Technologies. Retrieved 2025-06-12.

- ^ Kahng, Andrew B. (2000). "Classical floorplanning harmful?". Proceedings of the 2000 international symposium on Physical design. ISPD '00. Association for Computing Machinery. pp. 207–213. doi:10.1145/332357.332401. ISBN 1-58113-191-7. Retrieved 2025-06-12.

- ^ Liu, Chen-Wei and Chang, Yao-Wen (2024-09-01). "Physical Design: Methodologies and Developments". arXiv:2409.04726 .

{{cite arXiv}}: CS1 maint: multiple names: authors list (link) - ^ a b

VLSIPD4 (2023-04-23). "Floorplanning in Physical Design". Medium. Retrieved 2025-06-06.

{{cite web}}: CS1 maint: numeric names: authors list (link) - ^ VLSI‑Talks (January 2023). "FLOORPLAN - VLSI TALKS". VLSI TALKS. Retrieved 2025-06-12.

- ^ Lin, Ruei-Bin; Chiang, Yi-Xiu (2019). Impact of Double-Row Height Standard Cells on Placement and Routing. 20th International Symposium on Quality Electronic Design (ISQED). Santa Clara, CA, USA: IEEE. pp. 317–322. doi:10.1109/ISQED.2019.8697712. Retrieved 2025-06-12.

- ^ Liu, Chen-Wei; Chang, Yao-Wen (2006). Floorplan and power/ground network co-synthesis for fast design convergence. 2006 International Symposium on Physical Design. ISPD '06. San Jose, California, USA: Association for Computing Machinery. pp. 86–93. doi:10.1145/1123008.1123026. Retrieved 2025-06-12.

- ^ Funke, Julia; Hougardy, Stefan; Schneider, Jan (2016). "An exact algorithm for wirelength optimal placements in VLSI design". Integration: The VLSI Journal. 52: 355–366. doi:10.1016/j.vlsi.2015.07.001. Retrieved 2025-06-12.

- ^ a b "The Electrical Engineering Handbook", Richard C. Dorf (1997) ISBN 0-8493-8574-1

- ^ Sarrafzadeh, M, "Transforming an arbitrary floorplan into a sliceable one", Proc. 1993 IEEE/ACM International Conference on Computer-Aided Design (ICCAD-93), pp. 386-389.